Coautor: Ramesh Radhakrishnan, Distinguido Ingeniero, Oficina del CTO, Servidor y Sistemas de Infraestructura en Dell EMC

En los últimos años ha aumentado el interés por el uso de aceleradores en los servidores estándar para mejorar el rendimiento de la carga de trabajo. Comenzó con las GPU para acelerar la IA/ML y ahora incluye FPGAs, SMART-NICs en servidores y otros aceleradores incorporados de baja potencia en los dispositivos finales para el análisis de datos, la inferencia y el aprendizaje de la máquina. En este blog, compartimos nuestra perspectiva sobre estas nuevas clases de aceleradores emergentes y el papel que desempeñarán en la creciente adopción de la IoT y la 5G a medida que las cargas de trabajo se distribuyen desde el borde al centro de datos y a la nube.

La Década de los Datos verá la transformación del paisaje informático y la proliferación de las tecnologías de aceleración

Con el crecimiento exponencial de los datos, un número cada vez mayor de dispositivos de IoT en el borde, y todas las industrias que están pasando por la transformación digital, el futuro de la informática está impulsado por la necesidad de procesar los datos de manera rentable, maximizar el valor de los negocios y ofrecer un retorno de la inversión. La Década de los Datos está dando lugar a arquitecturas que procesan los datos cerca de la fuente de generación de datos y sólo envían información a través de redes de larga distancia que requieren almacenamiento o análisis de nivel superior. Los nuevos casos de uso en torno a vehículos autónomos (coches autopropulsados, aviones no tripulados), proyectos de ciudades inteligentes y fábricas inteligentes (robots, control de equipos de misión crítica) requieren que el procesamiento de datos y la toma de decisiones se realicen más cerca del punto de generación de datos debido a los requisitos de misión crítica, baja latencia y tiempo casi real de estos despliegues.

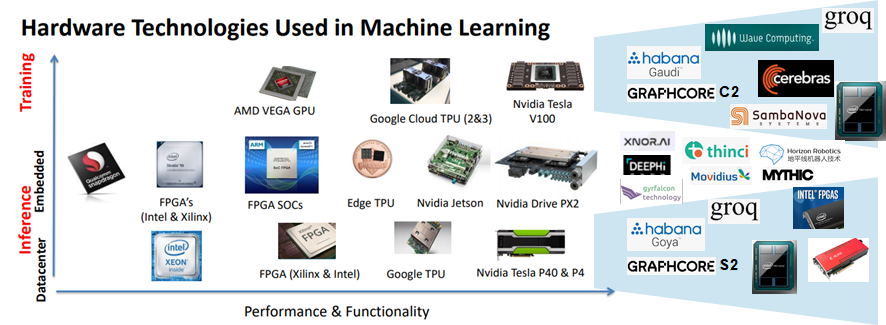

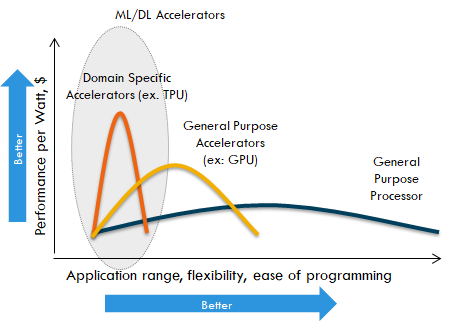

Las arquitecturas de computación de borde están emergiendo con infraestructura de computación y aplicaciones distribuidas a través del borde a la nube. Esta tendencia conducirá a una gama de arquitecturas de computación optimizadas a lo largo de diferentes vectores – capacidad de computación de punto flotante masivamente paralelo en el centro de datos para entrenar modelos complejos de redes neuronales (donde la energía no es una preocupación) a dispositivos de alta eficiencia energética que pueden inferir los modelos de redes neuronales desplegados en el borde. Esto lleva a una explosión cámbrica de dispositivos que serán usados como parte de este continuo de nube a borde.

En el frente del procesador, en los últimos diez o quince años las arquitecturas tradicionales de la CPU han evolucionado a un número cada vez mayor de núcleos y memoria, pero la E/S y el ancho de banda de la memoria no han seguido el ritmo. La ampliación de la memoria y el ancho de banda de E/S es crítica para procesar conjuntos de datos masivos en el centro de datos y la transmisión en tiempo real en el borde. Estos factores están llevando a la evolución de la aceleración del hardware tanto en los dispositivos de red como en los de almacenamiento para optimizar el flujo de datos a través de la CPU, la memoria y los subsistemas de E/S a nivel de todo el sistema. El crecimiento del procesamiento de datos ha llevado al uso de aceleradores dedicados para cargas de trabajo de Inteligencia Artificial (IA), Aprendizaje Automático (ML) y Aprendizaje Profundo (DL). Estos aceleradores realizan cómputos en paralelo y una ejecución más rápida de los trabajos de IA en comparación con las arquitecturas tradicionales de CPU. Proporcionan un soporte dedicado para la ejecución eficiente de las matemáticas matriciales que dominan las cargas de trabajo de ML/DL. Se dispone de múltiples modos de precisión numérica más allá de lo que está disponible en las CPU (BFLOAT16, Mixed Precision Floating Point) para acelerar masivamente un amplio espectro de aplicaciones de IA.

A continuación, echamos un vistazo a cinco áreas clave en las que los aceleradores jugarán un papel fundamental. Las tecnologías de los aceleradores juegan un papel clave en el despliegue de la tecnología 5G y los servicios asociados (que incluyen la IA, la AR/VR y el intercambio de contenido entre otros) en cada etapa del espectro de computación.

- Cargas de trabajo de la IA / Soluciones: Además de los jugadores tradicionales para los ASIC de aprendizaje automático (a saber, Nvidia, Intel y Google), están surgiendo nuevas empresas que se centran en un mayor rendimiento, menor potencia y áreas de aplicación específicas. Algunos ejemplos son Graphcore, Groq, Hailo Technologies, Wave Computing y Quadric. Están impulsando optimizaciones para áreas específicas como el procesamiento del lenguaje natural, AR/VR, reconocimiento de voz y visión por computador. Algunos de estos ASIC de IA se están centrando en la inferencia y en integrarse en dispositivos finales como vehículos autónomos, cámaras, robótica y aviones teledirigidos para impulsar el procesamiento de datos y la toma de decisiones en tiempo real.

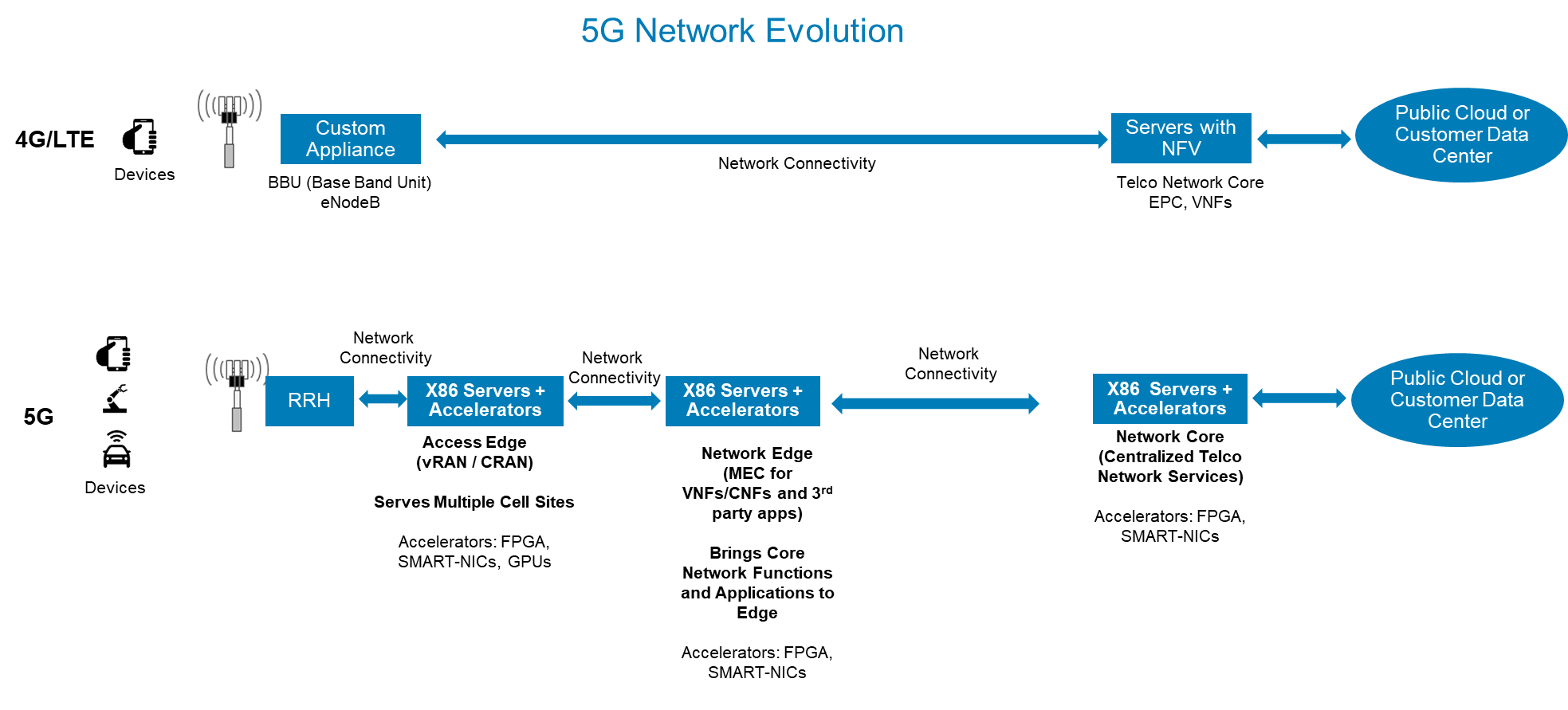

- Borde de acceso 5G: La evolución de las redes celulares a 5G está dando como resultado la virtualización y desagregación de la arquitectura de la Red de Acceso Radioeléctrico (RAN) de las telecomunicaciones. El espectro inalámbrico de alta frecuencia 5G, las limitaciones de distancia y el aumento de las densidades celulares requieren una arquitectura RAN centralizada en la que las señales de radio de múltiples estaciones celulares se procesen en un lugar centralizado. El grupo de estándares industriales 3GPP y ORAN están definiendo la arquitectura y las especificaciones para garantizar la interoperabilidad entre los proveedores de RAN. La unidad de procesamiento de RAN centralizada utiliza servidores estándar listos para usar y técnicas de virtualización junto con aceleradores para desacoplar el procesamiento del plano de control y el plano de datos. El plano de control se ejecuta en un servidor virtualizado llamado CU (Unidad Central) y el procesamiento del plano de datos se realiza en un servidor estándar (llamado DU o Unidad Distribuida) con el procesamiento de paquetes de radio descargado a una tarjeta aceleradora. Estas tarjetas aceleradoras son típicamente una FPGA o un ASIC personalizado con redes sensibles al tiempo (TSN) y otras capacidades de procesamiento de paquetes. Compañías de software como Radisys y Altiostar están entregando software de plano de control RAN que descarga el procesamiento de radiopaquetes a las tarjetas aceleradoras.

- Borde de la red 5G: La alta velocidad, la baja latencia y el aumento del número de conexiones de dispositivos soportados por las redes 5G están dando lugar a un nuevo conjunto de casos de uso en torno a la AR/VR, los juegos, la entrega de contenidos y el intercambio de contenidos. Esto requiere trasladar las aplicaciones de terceros al borde de la red junto con las capacidades de corte de la red para distinguir entre los diferentes tipos de tráfico y los acuerdos de nivel de servicio (SLA) asociados. Esto transforma el borde de la red de telecomunicaciones en una nube distribuida que ejecuta aplicaciones de desarrolladores y proveedores de servicios de terceros. El traslado de las cargas de trabajo al borde de la red también requiere los servicios subyacentes de infraestructura de red y almacenamiento para garantizar la seguridad de la red y el almacenamiento de datos. Los VNF de las telecomunicaciones (por ejemplo, EPC, BNG) y los servicios de red (por ejemplo, cortafuegos, equilibradores de carga, IPSEC) se están trasladando al borde de la red para permitir el alojamiento de nuevas cargas de trabajo. A fin de liberar los núcleos de CPU del servidor para aplicaciones de terceros y ofrecer funciones avanzadas de seguridad de la red (por ejemplo, inspección profunda de paquetes, cifrado, corte de redes, análisis), los servicios subyacentes de infraestructura de la red se están descargando en tarjetas aceleradoras denominadas SMART-NIC. Estas SMART-NICs contienen una funcionalidad estándar de NIC junto con núcleos de CPU de bajo consumo y bloques de aceleración de hardware para el procesamiento de la red. También proporcionan una interfaz de plano de datos programable para que los VNFs de Telco descarguen el procesamiento de plano de datos de la red en el hardware. El grupo de estándares de la industria 3GPP está definiendo la arquitectura y los estándares para CUPS (Control Plane and User Plane Separation). Muchas compañías de adaptadores de red como Intel, Mellanox, Broadcom, Netronome y empresas emergentes se están centrando en estos adaptadores de aceleración de red. También hay tarjetas aceleradoras personalizadas que están surgiendo para centrarse específicamente en el almacenamiento en caché de contenidos y el análisis de vídeo (juegos, AR/VR).

- Computación IoT / Edge: La IoT está impulsando la computación de tipo servidor para acercarse a los dispositivos finales. Empresas de todos los tamaños están experimentando una transformación digital para automatizar sus operaciones y servir mejor a sus clientes. Esto está resultando en despliegues híbridos/multi-nube más cercanos a sus usuarios finales (clientes, empleados o dispositivos), ya sea en forma preeminente o en una instalación de co-ubicación. Al igual que en el borde de la red, los aceleradores (FPGAs, SMART-NICs, GPUs) juegan aquí un papel clave para la aceleración de los servicios de infraestructura y para acelerar el procesamiento de datos para la IA/ML.

- Centro de datos centralizado / Nube: La mayoría de las implementaciones en el borde consisten en un entorno híbrido/multi-nube donde el procesamiento se realiza como una combinación de procesamiento casi en tiempo real en el borde y procesamiento en el backend en un centro de datos centralizado o en una nube pública. Un centro de datos centralizado (o nube pública) alberga la infraestructura para el aprendizaje profundo, el almacenamiento y el procesamiento de datos. La infraestructura de aprendizaje profundo hace un uso cada vez mayor de las GPU de gama alta y de los ASIC de aprendizaje profundo de alto rendimiento que están surgiendo. Con el aumento de las velocidades de la red (50G/100G y más), la memoria persistente, las unidades de NVMe de alto rendimiento y los crecientes requisitos de seguridad (cifrado, compresión, inspección profunda de paquetes, análisis de redes), los servicios de red están utilizando aceleradores para descargar las funciones del plano de datos de la red en el hardware. Esto permite que todas estas funciones se realicen a velocidad de cable y que los servicios de red se encadenen. Las pilas de almacenamiento definidas por el software también están evolucionando para hacer uso de aceleradores para funciones avanzadas como la deduplicación, la codificación de borrado, la compresión, la encriptación y para escalar para ofrecer el mayor rendimiento con memoria persistente, unidades NVMe y redes de alto rendimiento.

Además de las oportunidades mencionadas anteriormente en torno a los aceleradores, hay una cantidad cada vez mayor de datos que se almacenan en los sistemas de almacenamiento. Con el fin de proporcionar un acceso inteligente a los datos, los futuros dispositivos de almacenamiento están evolucionando para ser programables, donde la FPGA y otras técnicas de aceleración de hardware están integradas en el subsistema de la unidad para analizar los datos en el lugar y sólo proporcionan el resultado a la aplicación. Estas unidades tendrán capacidades para ejecutar código de terceros y se denominan comúnmente almacenamiento computacional. Optimiza la transferencia de datos a través de la red, donde se pueden analizar grandes vídeos e imágenes, y se pueden realizar consultas a la base de datos justo donde se almacenan los datos. Los grandes sistemas de almacenamiento también están incorporando aceleradores, virtualización y marcos nativos de la nube en el sistema de almacenamiento para procesar datos y alojar aplicaciones analíticas de terceros.

Este uso de la aceleración de hardware para el aprendizaje automático, los servicios de red y los servicios de almacenamiento es sólo el comienzo de un cambio en la arquitectura del sistema. La próxima evolución impulsará flujos de datos más optimizados a través de varios aceleradores para que los datos puedan fluir entre la red, el almacenamiento y las GPU directamente sin involucrar a las CPU x86 y la memoria del host. Esto será cada vez más importante en las futuras arquitecturas de servidores desagregados y componibles, en las que un servidor lógico se compone de grupos independientes de CPU, memoria, adaptadores de red, unidades de disco y GPU conectados con un tejido de alto rendimiento.

Se está investigando para mejorar los aceleradores de aprendizaje de la máquina para capacidades como el aprendizaje de refuerzo y la IA explicable. Los futuros aceleradores de ML apoyarán las capacidades para permitir el entrenamiento localizado en el borde para mejorar aún más la toma de decisiones para los conjuntos de datos localizados. Los aceleradores en el borde también deben tener en cuenta las condiciones ambientales en el lugar de despliegue. Muchos despliegues en el borde necesitan una infraestructura robusta, ya que se despliega ya sea en un entorno exterior (lado de la calle, aparcamiento o fuera de un edificio) o en un entorno de almacén (por ejemplo, comercio minorista, fábrica). Es necesario tener en cuenta los requisitos de energía, térmicos y de factor de forma para construir la infraestructura robusta que contiene aceleradores para los despliegues en el borde.

Las empresas que innoven en esta arquitectura a nivel de sistema para cargas de trabajo de próxima generación ganarán al conducir a los clientes hacia la transformación digital, el borde y la 5G. En Dell EMC, estamos muy centrados en este uso evolutivo de los aceleradores, la infraestructura de TI reforzada y las optimizaciones a nivel de sistema. Consulte el reciente anuncio de Dell Technologies sobre la plataforma informática reforzada PowerEdge XE2420, el centro de datos modular Dell EMC Micro 415 y la plataforma de datos de transmisión de Dell EMC.

Para obtener más información sobre los servidores PowerEdge, visite la página de servidores PowerEdge, la página de soluciones de aceleradores de Dell EMC, la página de soluciones informáticas Dell EMC Edge o únase a la conversación en Twitter.